Komplementäre Resisitive Schalter für den Computer der Zukunft

Jahrelang ging es bei der Entwicklung neuer Computer in erster Linie um höhere Speicherdichten und höhere Taktraten, wobei die Verlustleistung pro Fläche immer weiter anstieg. Die Verbesserung der Energieeffizienz stellt inzwischen, nicht nur für mobile Anwendungen, eine der größten Herausforderung für die Entwicklung neuer Computersysteme dar. Es gibt zwei Hauptgründe für die hohen Verluste in heutigen Computersystemen: erstens die verwendeten Komponenten und zweitens die Computerarchitektur als solches. So wird in heutigen Arbeitsspeichern (DRAM) die digitale Information in Form von Ladung auf Kondensatoren gespeichert, die in kurzen Zeitabständen wieder aufgeladen werden müssen. Diese Art der Informationsspeicherung ist flüchtig und führt zu hohen Verlusten. Die verwendete Computerarchitektur heutiger Computer basiert außerdem auf der strikten Trennung von Speicher (Arbeitsspeicher) und Logik (Prozessor). Diese Trennung führt ebenfalls zu hohen Verlusten, da ein permanenter Informationsaustausch zwischen Speicher und Logik stattfinden muss.

Ein Paradigmenwechsel hin zu neuen Computerarchitekturen und die Entwicklung neuartiger Speicher- und Logikelementen wird deshalb seit einigen Jahren gefordert und durch starke Forschungsaktivitäten begleitet [1-5].

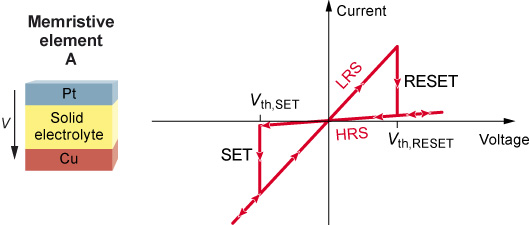

Als vielversprechendes Speicher- und Logikelement hat sich dabei der resistive Schalter herausgestellt. Dieses memristive Element speichert die Information als hohen (HRS) bzw. niedrigen (LRS) Widerstandswert und basiert somit, anders als der DRAM, nicht auf der Speicherung von Ladung. Das memristive Element behält auch ohne äußere Energiezufuhr den gespeicherten Zustand, ist also nichtflüchtig. Durch das Anlegen einer negativen Spannung schaltet das Element vom Zustand HRS in den Zustand LRS und kann durch Anlegen einer positiven Spannung wieder in den Zustand HRS überführt werden (Abb. 1).

Als neuartige Computerarchitektur wird eine modulare Struktur vorgeschlagen, die im Wesentlichen auf rekonfigurierbaren Blöcken, ähnlich wie in heutigen FPGAs (Field Programmable Gate Array), basiert. Im einfachsten Fall besteht ein solcher Block aus einer Matrix gekreuzter Leiterbahnen (Crossbar Array), an deren Kreuzungspunkten die neuartigen Speicher- und Logikelemente eingebaut werden (Abb. 2).

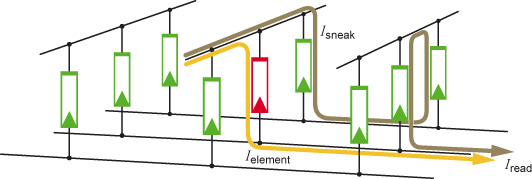

Als Speicher- und Logikelement der Wahl wurde bisher der resistive Schalter angesehen, da er u.a. die Anforderungen an Skalierbarkeit, Geschwindigkeit und Energieeffizienz gut erfüllt. Ein großer Nachteil ergibt sich allerdings durch Einsatz von resistiven Schaltern in Crossbar Arrays: Es treten unerwünschte Strompfade auf, wie Abb. 3 gut zu erkennen. Diese parasitären Strompfade verringern die gute Energieeffizienz der einzelnen Schalter sehr stark. Die resultierende maximale Crossbar-Größe liegt dann auch nur bei acht mal acht, viel zu klein für reale Anwendungen.

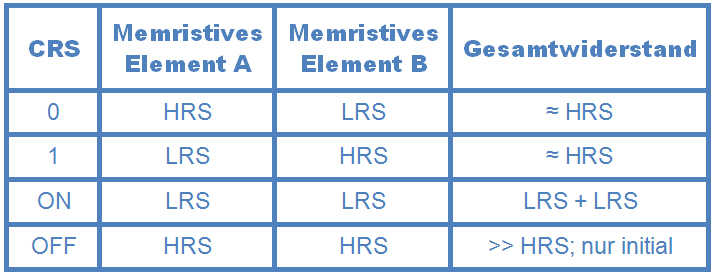

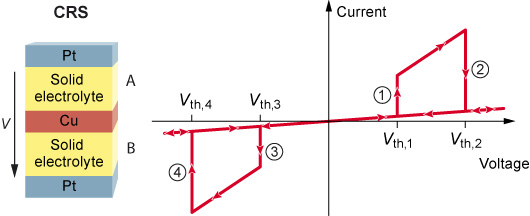

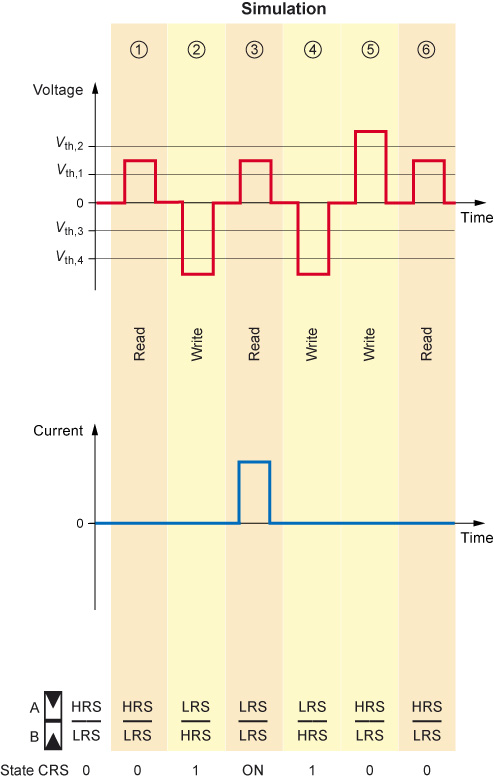

Dieses Problem konnte in einer aktuellen Forschungsarbeit gelöst werden, indem die resistiven Schaltern durch komplementäre resisitive Schalter ersetzt wurden [6]. Die komplementären resisitiven Schalter (CRS) bestehen aus zwei antiseriell (komplementär) verschalteten resistiven Schaltern (Abb. 4). Eine CRS-Zelle ist wie ein resistiver Schalter ein zweipoliges Bauelement, das sich in einem von vier möglichen Zuständen befinden kann (Tab. 1). Der Zustand 'OFF' ist nur bei noch nicht initialisierten Zellen anzutreffen und wird im Folgenden nicht weiter betrachtet. Die Zustände '0' und '1' stellen die eigentlichen Speicherzustände dar und der Zustand 'ON' tritt immer nur kurzeitig beim Abfragen (Lesen) des Speicherzustands auf. Eine CRS-Zelle zeichnet sich dadurch aus, dass die inneren Speicherzustände '0' und '1' nicht am Widerstand erkennbar sind, da sich in beiden Fällen ein hoher Widerstand ergibt. Es können sich somit keine parasitären Strompfade ausbilden, da dafür Zellen mit niedrigem Widerstand im Crossbar vorliegen müssten. Um die Information ('0' oder '1') der einzelnen CRS-Zellen abzufragen wird eine Lesespannung angelegt, die die CRS-Zelle in den Zustand 'ON' überführt (falls Zustand '1' vorlag) bzw. im Zustand '0' belässt (falls Zustand '0' vorlag) (Abb. 5). Durch dieses selektive Schalten in den Zustand 'ON' wird die Information gelesen und dadurch gleichzeitig zerstört (destruktives Lesen). Deshalb muss nach dem Lesen der vorherige Zustand der Zelle wieder eingeschrieben werden. Generell wird zum Schreiben des Zustands '1' eine negative Spannung benötigt (<Vth,4) und zum Schreiben einer '0' eine positive Spannung (>Vth,2) benötigt. Detaillierte Informationen zur Herstellung und Integration von CRS-Zellen sind in [8] zu finden.

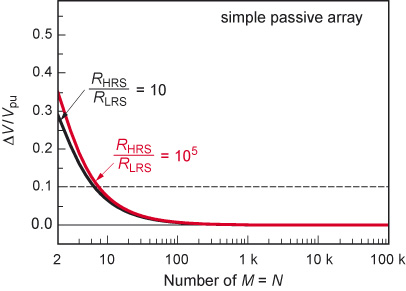

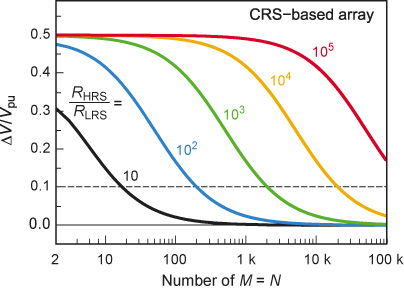

Um die Überlegenheit des CRS-Konzepts zu verdeutlichen wird ein Crossbar Array mit resistiven Schaltern mit einem Crossbar Array mit CRS-Zellen verglichen. Dabei wird jeweils das ungünstigste (worst case) Szenario betrachtet. Für ein Crossbar Array mit herkömmlichen memresistiven Elementen sind in diesem Fall alle Elemente niederohmig (LRS). Möchte man jetzt ein beliebiges Element lesen, d.h. den Zustand LRS oder HRS bestimmen, ist der in einem angeschlossenen Leseverstärker detektierbare Spannungshub ΔV die relevante Kenngröße. Geht man davon aus, dass der normierte Spannungshub mindestens zehn Prozent betragen muss, dann sind mit diesem Crossbar Arrays, wie bereits erwähnt, nur Strukturen der Größe acht mal acht möglich (Abb. 6). Verwendet man hingegen CRS-Zellen und betrachtet ebenfalls das ungünstigste Szenario (bedeutet hier: alle Zellen in einer Reihe 'ON'), dann ergibt sich ein ganz anderes Bild. Durch die Verhinderung der parasitären Strompfade ist der normierte Spannungshub auch für sehr große Crossbar Arrays noch gut detektierbar, was Arraygrößen von 100000 mal 100000 in den Bereich des Möglichen rückt (Abb. 7).

Die Verwendung von CRS-Zellen als Speicher- und Logikelement ermöglicht somit den Betrieb von großen Crossbar Arrays und könnte die Grundlage für einen Paradigmenwechsel hin zu einer neuen energieeffizienteren Computerarchitektur sein.

Tab. 1 Schaltzustände

Abb. 1 Memristives Element

Hier ist die I-V-Charakteristik eines memresistiven Elements dargestellt. Befindet sich der Schalter zunächst im niederohmigen Zustand (LRS), so kann er durch Anlegen einer positiven Spannung V>VRESET in den hochohmigen Zustand (HRS) überführt werden. Analoges gilt für das Anlegen einer negativen Spannung. Hier schaltet das Element für Spannungen kleiner als VSET wieder zurück in den LRS. Ein solches Element wird in der Literatur als bipolarer resistiver Schalter bezeichnet.

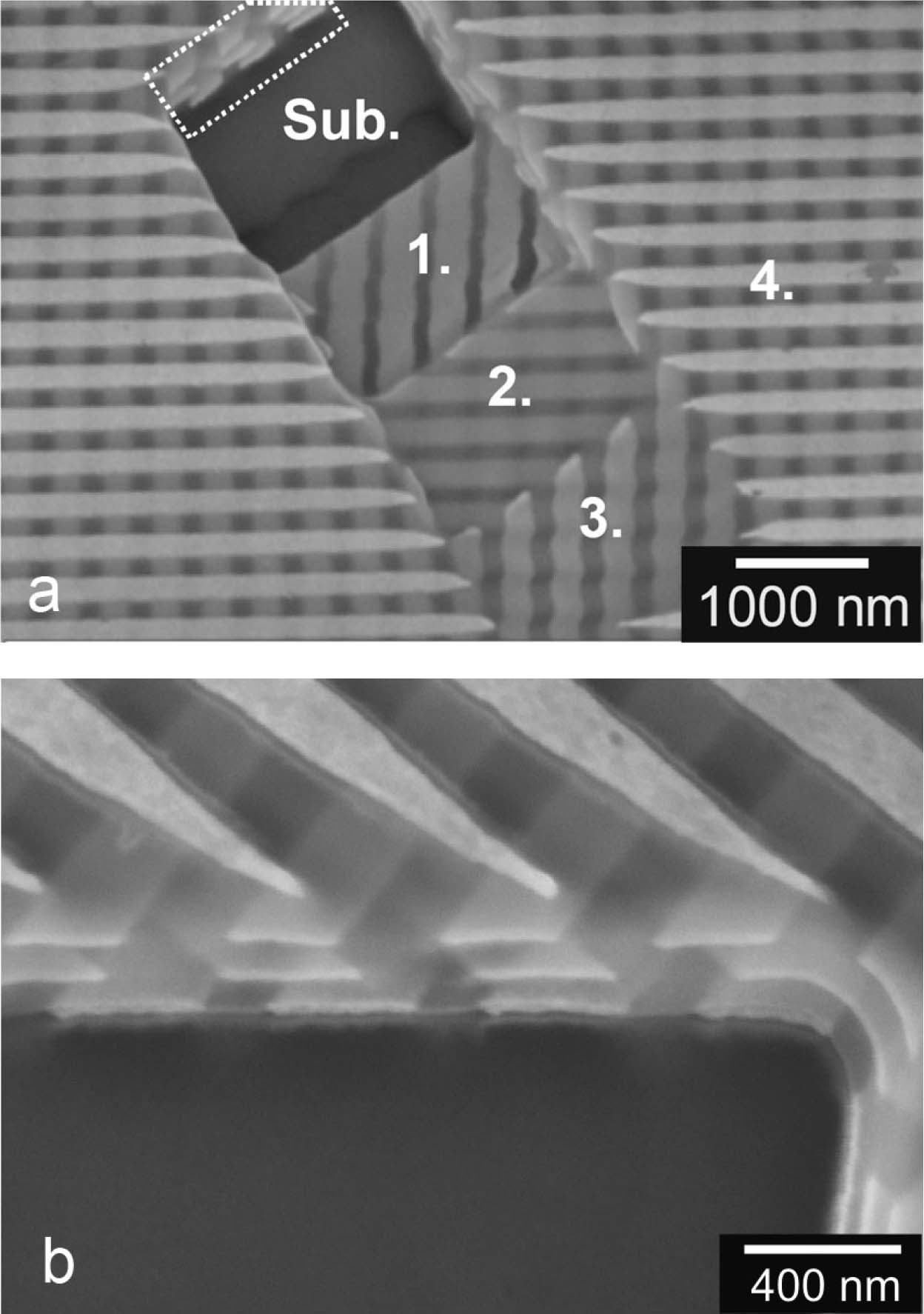

Abb. 2 SEM-Bild eines Crossbar Arrays

Diese Abbildung zeigt in a. eine Multi-Layer-Struktur, wie sie auch für zukünftige Crossbar-Array-basierte Computerarchitekturen verwendet werden könnte. Durch den regelmäßigen Aufbau sind solche Strukturen verhältnismäßig einfach in der Nanometerskala herstellbar. In b. ist ein Ausschnitt aus a. vergrößert dargestellt. [7]

Abb. 3 Parasitäre Strompfade

Die Abbildung zeigt einen Ausschnitt aus einem Crossbar Array. In diesem Beispiel ist nur das rote Element in der Mitte des Crossbar Arrays hochohmig, alle anderen niederohmig. Zusätzlich zu dem erwünschten Strompfad durch das Element in der Mitte gibt es weitere Strompfade (hier ist nur ein weiterer eingezeichnet) die einen zusätzlichen, parasitären Stromfluss erzeugen.

Abb. 4 I-V-Charakteristik einer CRS-Zelle

Der prinzipielle Aufbau einer CRS-Zelle besteht aus zwei antiseriell verschalteten memristiven Elementen A und B. Der Verlauf der Kennlinie ergibt sich aus der Betrachtung der Spanungsabfälle über den einzelnen Elementen A und B. Geht man davon aus Element A zunächst im LRS und B im HRS ist (Zustand '1'), so fällt der Großteil der Spannung über Element B ab. Erst wenn Vth,1 überschritten wird, schaltet Element B ebenfalls in LRS (Zustand 'ON'). Durch den nun wirksamen Spannungsteiler wird die Zelle A erst beim Überschreiten der Spannung Vth,2 ausgeschaltet (Zustand '0') . Bis zu negativen Spannungen von Vth,3 verbleibt die Zelle im Zustand '0' und schaltet erst bei Spannungen V < Vth,3 in den Zustand 'ON'. Durch die Aufteilung der Spannung auf beide Elemente schaltet Element B erst bei Spannungen kleiner als Vth,4 zurück in den Zustand '1'. (Zum leichteren Verständnis der Funktion gibt es hier auch ein interaktives CRS-Modell.)

Abb. 5 Pulsbetrieb einer CRS

Die CRS-Zelle ist zunächst im Zustand '0'. Im ersten Schritt wird die Zelle gelesen, was keine Stromantwort zur Folge hat, da sich die Zelle im Zustand '0' befindet. In Schritt zwei wird eine '1' geschrieben und anschließend, in Schritt drei gelesen. Dies resultiert in einer Stromantwort; die Zelle schaltet in den Zustand 'ON'. Durch das Zurückschreiben des Zustands '1' in Schritt vier wird die Information in der Zelle wiederhergestellt. Schreibt man wieder eine '0' (Schritt fünf) und führt abermals eine Leseoperation (Schritt sechs) durch, so erhält man wieder das Ergebnis aus Schritt 1 (keine Stromantwort).

Abb. 6 Normierter Spannungshub bei Verwendung von memristiven Elementen

Auf der x-Achse ist die Arraygröße (N Spalten, M Zeilen) aufgetragen, auf der y-Achse der normierte Spannungshub. Für das betrachtet Worst-Case-Szenario (alle Elemente in LRS) wird deutlich das bei minimalen Spannungshub von 10 % nur Arraygrößen von N = 8 mal M = 8 möglich sind. Auch durch Erhöhung des RHRS zu RLRS Verhältnisses kann die mögliche Arraygröße nicht wesentlich erhöht werden.

Abb. 7 normierter Spannungshub bei Verwendung von CRS-Zellen

Auf der x-Achse ist die Arraygröße (N Spalten, M Zeilen) aufgetragen, auf der y-Achse der normierte Spannungshub. Für das betrachtet Worst-Case-Szenario (alle Zellen einer Reihe im 'ON'-Zustand) wird deutlich, dass sehr große Crossbar Arrays möglich sind. Mit realistischen RHRS zu RLRS Verhältnissen können N = 100000 mal M = 100000 große Arrays aufgebaut werden.

- [1] R. Waser. Nanoelectronics and Information Technology, 2nd, Corrected Edition. Wiley-VCH (2005).

- [2] Szot, K., Speier, W., Bihlmayer, G. & Waser, R. Switching the electrical resistance of individual dislocations in single-crystalline SrTiO3. Nat. Mater. 5, 312-20 (2006).

- [3] Waser, R. & Aono, M. Nanoionics-based resistive switching memories. Nat. Mater. 6, 833-840 (2007).

- [4] Borghetti, J., Snider, G. S., Kuekes, P. J., Yang, J. J., Stewart, D. R. & Williams, R. S. 'Memristive' switches enable 'stateful' logic operations via material implication. Nature 464, 873-876 (2010).

- [5] Strukov, Dmitri B., Snider, Gregory S., Stewart, Duncan R. & Stanley Williams, R. The missing memristor found. Nature 453, 80-83 (2008).

- [6] Linn, E., Rosezin, R., Kuegeler, C. & Waser, R. Complementary resistive switches for passive nanocrossbar memories. Nature Materials 9, 403-406 (2010).

- [7] Meier, M. Entwicklung einer Nanotechnologie-Plattform für die Herstellung Crossbar-basierter Speicherarchitekturen (Forschungszentrum Jülich GmbH Zentralbibliothek, Verlag, 2009).

- [8] R. Rosezin, E. Linn, L. Nielen, C. Kügeler, R. Bruchhaus, and R. Waser, Integrated Complementary Resistive Switches for Passive High-Density Nanocrossbar Arrays, IEEE Electron Device Letters, in press (2011).

Linn, E., Rosezin, R., Kuegeler, C. & Waser, R.